# **JW1530**

# High Efficiency Off-line CV Regulator

Parameters Subject to Change Without Notice

# **DESCRIPTION**

The JW<sup>®</sup>1530 is a high efficiency low cost off-line constant voltage regulator for Buck and Buck-Boost topology with 700V MOSFET integrated.

JW1530 can output 5V default voltage with few external components, which decreases the system cost. In light load condition, JW1530 operates in green mode, in which the inductor peak current and the switching frequency is lower than that of full load to improve the system efficiency and the reference voltage is decreased to ensure good load regulation.

JW1530 has multi-protection functions which largely enhance the safety and reliability of the system, including VDD under-voltage Lockout (UVLO), short circuit protection (SCP), pulse-by-pulse current limit, over load protection (OLP) and over-temperature protection (OTP).

Company'sLogo is Protected, "JW" and "JOULWATT"areRegistered Trademarks of JoulWatt technology Inc.

# **FEATURES**

- Ultra low system BOM cost

- Integrated with 700V, low Rdson MOSFET

- 5V default output voltage

- Peak current mode control

- Built-in 30KHz Oscillator with frequency Jittering

- High efficiency over wide operating range

- VDD UVLO

- Short circuit protection

- Pulse-by-pulse current limit

- Over temperature protection

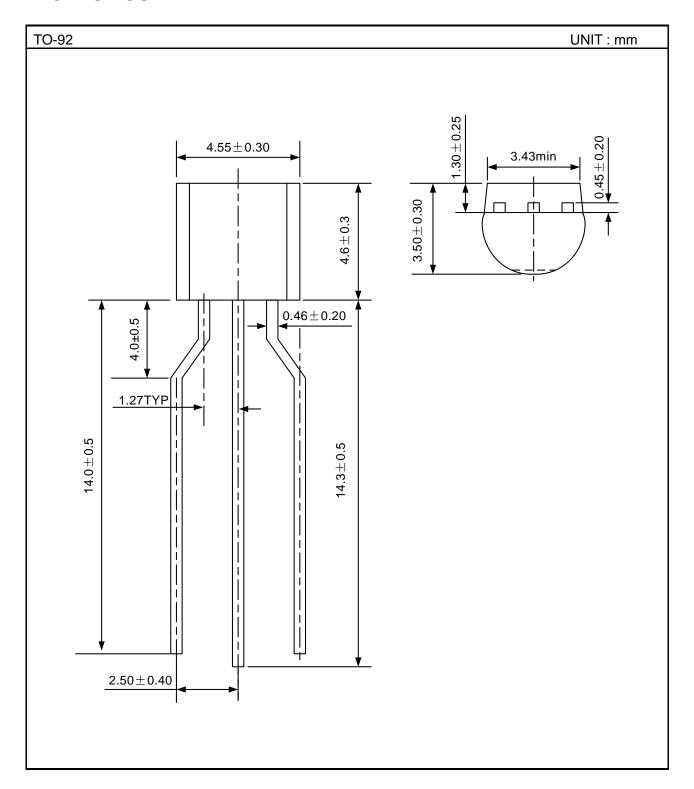

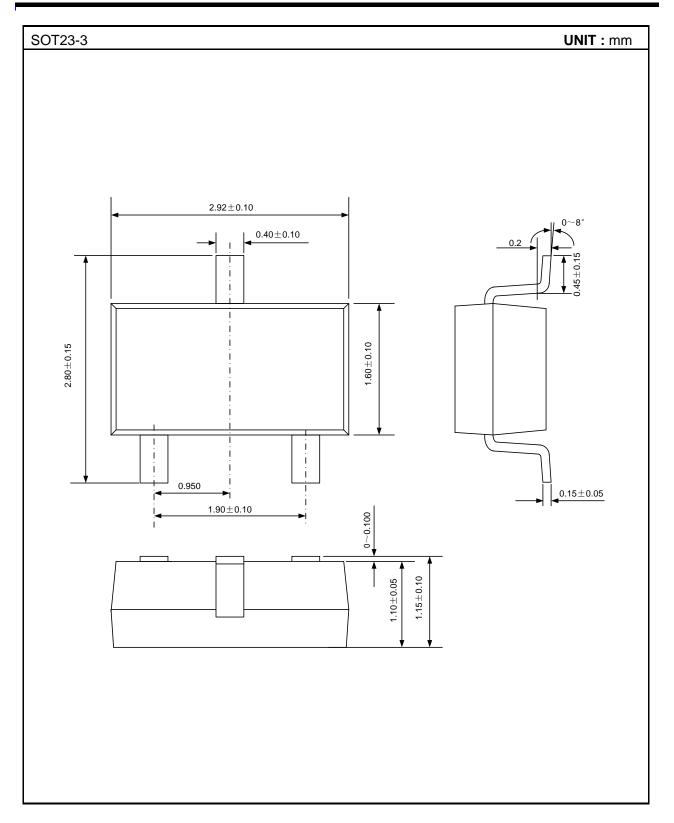

- TO-92,SOT23-3 package

# **APPLICATIONS**

- Homeappliance

- Standby power

- Consumer electronics

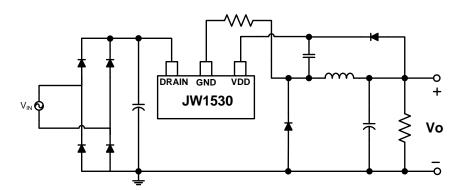

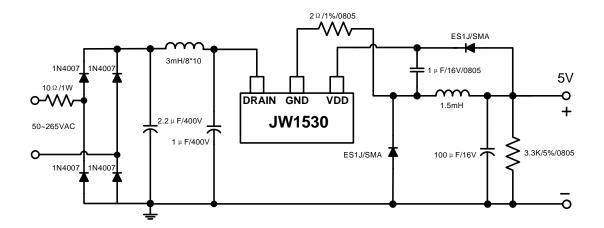

# TYPICAL APPLICATION

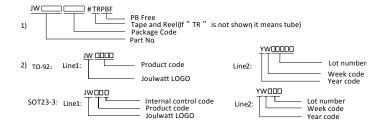

# **ORDER INFORMATION**

| DEVICE <sup>1)</sup> | PACKAGE | TOP MARKING <sup>2)</sup> |

|----------------------|---------|---------------------------|

| 1VA/4 F 20TOC#TDDF   | TO-92   | JW1530                    |

| JW1530TOC#TPBF       | 10-92   | YW□□□□                    |

| JW1530SOTF#TRPBF     | SOT23-3 | JWMD□                     |

| JWT550501F#IKPBF     | 30125-3 | YW□□□                     |

#### Notes:

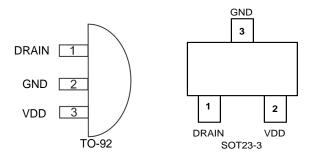

# **PIN CONFIGURATION**

# **TOP VIEW**

# **ABSOLUTE MAXIMUM RATING**<sup>1)</sup>

| VDD Voltage                           | 6V             |

|---------------------------------------|----------------|

| DRAIN Voltage                         | 700V           |

| Junction Temperature <sup>2) 3)</sup> |                |

| Lead Temperature                      | 260°C          |

| Storage Temperature                   | 65°C to +150°C |

| ESD Susceptibility (Human Body Model) | 2.5kV          |

# RECOMMENDED OPERATING CONDITIONS

| DRAIN Voltage                                 | 450V     |

|-----------------------------------------------|----------|

| Operating Junction Temp (T <sub>J</sub> )40°C | to 125°C |

| Package | Recommended MAX Output Current (T <sub>J</sub> =125°C) <sup>4)</sup> |

|---------|----------------------------------------------------------------------|

| TO-92   | 180mA                                                                |

| SOT23-3 | 160mA                                                                |

| THERMAL PERFORMANCE <sup>5)</sup> | $	heta_{\!\scriptscriptstyle J\!A}$ | $	heta_{\!\scriptscriptstyle JC}$ |

|-----------------------------------|-------------------------------------|-----------------------------------|

| TO-92                             | 120                                 | 60°C/W                            |

| SOT23-3                           | 313.11                              | 44º ºC/W                          |

#### Note:

- 1) Exceeding these ratings may damage the device.

- 2) Guarantees robust performance from -40°Cto 150°C junction temperature. The junction temperature range specification is assured by design, characterization and correlation with statistical process controls.

- 3) Includes thermal protection that is intended to protect the device in overload conditions. Thermal protection is active when junction temperature exceeds the maximum operating junction temperature. Continuous operation over the specified absolutemaximum operating junction temperature may damage the device.

- 4) The maximum output current is recommended in the application according to chip junction temperature T<sub>J</sub>=125℃ (chip case temperature difference about 20℃). The maximum output current could be increased properly if the heat dissipation is better.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

| $T_A$ =25 °C, unless otherwise stated. |                     |           |      |      |      |            |

|----------------------------------------|---------------------|-----------|------|------|------|------------|

| ltem                                   | Symbol              | Condition | Min. | Тур. | Max. | Units      |

| VDD Quiescent Current                  | IQ                  | VDD=5V    |      | 110  | 140  | μA         |

| VDD Startup Voltage                    | $V_{DD\_ST}$        |           | 4.4  | 4.7  | 4.95 | V          |

| VDD Under Voltage Lockout              | $V_{DD\_UVLO}$      |           | 3.3  | 3.6  | 4    | V          |

| Output Reference Voltage               | $V_{REF}$           |           | 5.37 | 5.6  | 5.83 | V          |

| Peak Current Reference Voltage         | $V_{PK}$            |           | 490  | 520  | 550  | mV         |

| Power Mos Breakdown Voltage            | BV                  |           | 700  |      |      | V          |

| Power Mos Rdson                        | Rdson               |           |      | 15   |      | Ω          |

| Oscillator Frequency                   | f <sub>osc</sub>    |           | 23   | 30   | 36   | kHz        |

| Frequency Jittering Range              | Δf/f <sub>OSC</sub> |           | -5   |      | 5    | %          |

| Frequency Jittering Period             | $T_{Jit}$           |           |      | 15   |      | ms         |

| Maximum On Time 5)                     | T <sub>ONMAX</sub>  |           | 7    | 10   | 12.5 | μs         |

| Leading Edge Blanking Time             | T <sub>LEB</sub>    |           | 220  | 300  | 400  | ns         |

| Over Thermal Protection Threshold 5)   | Temp <sub>OTP</sub> |           |      | 150  |      | $^{\circ}$ |

# Note:

6) Guaranteed by design.

# **PIN DESCRIPTION**

| Pin<br>TO-92 | Name  | Description         |

|--------------|-------|---------------------|

| 1            | DRAIN | The drain of MOSFET |

| 2            | GND   | Chip ground         |

| 3            | VDD   | Power supply pin    |

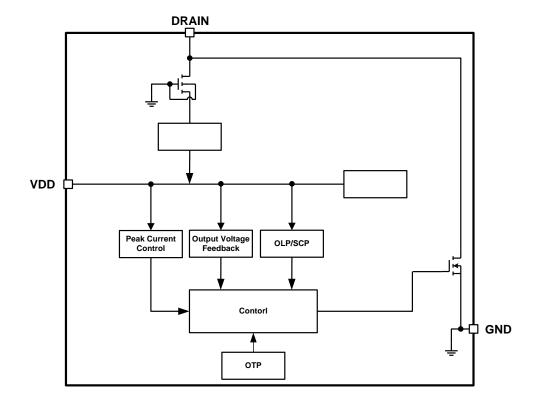

# **BLOCK DIAGRAM**

# **FUNCTIONAL DESCRIPTION**

JW1530 is a high efficiency low cost off-line constant voltage regulator for Buck and Buck-Boost topology.

# Start Up

JW1530 can be supplied fromMOS DRAIN directly. When the internal high voltage (HV) power souse charges VDD up to the  $V_{DD\_ST}$ , the gatedriver starts to switch. VDD will be powered by output voltage in steady state. Once the voltage of VDD is lower than  $V_{DD\_UVLO}$ , JW1530 stops switching.

#### **Peak Current Control**

JW1530 controls the inductor peak current of the inductor from theinformation of the current sensing resistor. The peak current can be calculated as:

Ipeak=V<sub>PK</sub>/R<sub>CS</sub>

Where,

V<sub>PK</sub> is the peak current reference voltage; R<sub>CS</sub> – the sensing resistor connected between chip GND and the VDD capacitor ground. Normally lpeak should be larger than 1.5\*lo\_max to avoid false triggered OLP.

# **Constant Voltage Control**

The output voltage is sensed by VDD pin. The MOS is turned off if the current of the inductor reaches the designed value, and turned on if VDD<VREF&fs  $\leqslant$  fosc. The switching frequency of JW1530 is fixed to fosc with  $\pm\,5\%$  Jitteringto improve the EMI performance when VDD<VREF. If VDD>VREF&fs  $\leqslant$  fosc, JW1530 keeps off until VDD<VREF again.

#### **Green Mode**

In light or no load condition, JW1530 operates in DCM which means the OFF timeis very long. JW1530 will reduce the peak current of the inductor to minimize the power loss. The longer Toff, the lower lpeak. Also, the reference voltage  $V_{\text{REF}}$  is decreased to ensure good load regulation.

# Short Circuit Protection (SCP)/ Over Load Protection (OLP)

In short circuit or over loadcondition, VDD can't be charged to  $V_{REF}$ . JW1530 will operate in auto-restart mode which is represented in the following description if VDD< $V_{REF}$  for 120ms.

#### **Auto-restart Mode**

JW1530 will enter auto-restart mode if SCP/OLP/OTP is triggered. The chip stops switching and the HV power source is disconnected until VDD decreases to 4.2V. If VDD is charged to 4.5V for 24 times, the system restarts.

# **Over Temperature Protection**

When internal temperature of the chip exceeds 150°C, JW1530 operates in auto-restart mode to help the chip cooling.

#### **PCB Design**

- 1. The VDD pin must be locally bypassed with a capacitor.

- Make the area of the power loop as small as possible in order to reduce the EMI radiation.

# **APPLICATION REFERENCE**

The reference design is suitable for non-isolated buck power supply default 5V output, using JW1530.

V<sub>IN</sub>: 50~265VAC

$V_{OUT}$ : 5V  $I_{OUT}$ : 150mA

# **PACKAGE OUTLINE**

# **IMPORTANT NOTICE**

Joulwatt Technology Inc. reserves the right to make modifications, enhancements, improvements,

corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Inc. does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Copyright © 2017JW1530 Incorporated.

All rights are reserved by Joulwatt Technology Inc.