# 4~10 Series Cell Battery Monitor and Protection IC

## DESCRIPTION

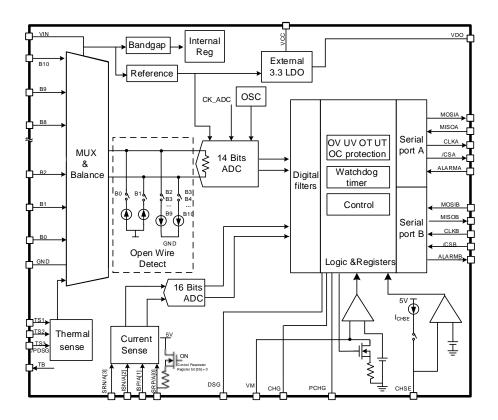

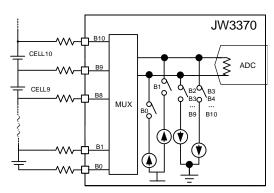

JW3370 is a multi-cell battery stack monitoring and protection IC that includes a 14-bit ADC for battery voltage and temperature sense, a 16-bit ADC for charge/discharge current sense.

JW3370 provides passive balance function for each cell and allows at most 3 consecutive cells being discharged simultaneously.

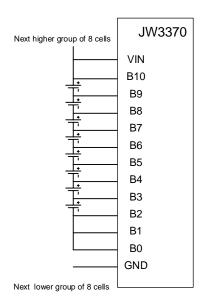

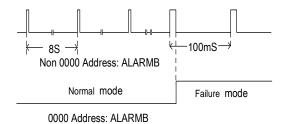

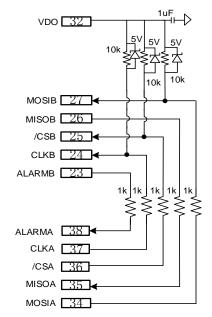

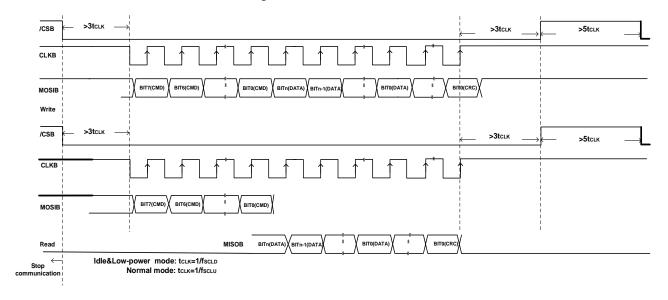

JW3370 communicates with external control unit via SPI interface. More JW3370 can operate in series to monitor long string battery.

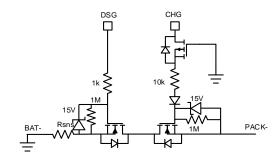

JW3370 integrates complete protection function including over/under voltage, over/under temperature, over charge/discharge current, short-circuit and open wire detection. When fault(s) happen, JW3370 will send alarm signal to inform host and shutdown CHG or DSG.

JW3370 integrated pre-charge and pre-discharge drivers for the deep discharge battery or some big capacitor load startup.

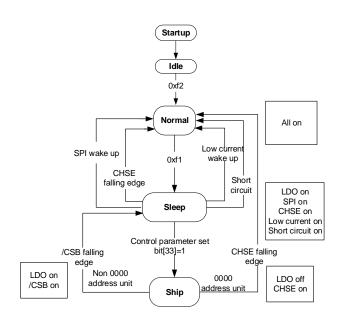

JW3370 supports both Sleep mode and Ship mode to achieve high efficiency with low power when charge/discharge current is minor.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered

Trademarks of Joulwatt Technology Co., Ltd.

## **FEATURES**

- Monitor 10 Series Cell Battery and Support Series Operation

- 14-bit ΔΣ ADC Samples Battery Voltage and Accuracy is ±5mV Typ. @2.3~4.3V

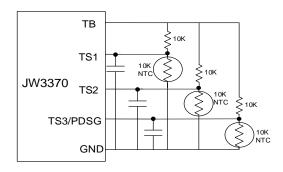

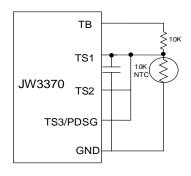

- Provide Filtering 3 Channels Thermal Sense and Accuracy is ±1°C (No Considering NTC Resistor Offset)

- Battery Over/Under Voltage Protection

- Battery Over/Under Temperature Protection

- Open Wire Connection Detection

- 10 Cells Passive Balance

On-Chip Passive Cell Balancing Switches

Provide Off-Chip Passive Balancing

- 16-bit ΔΣ ADC Senses Charge/Discharge Current and Accuracy is ±75μV Typ.@(-100 mV ~100mV)

±150μV Typ.@(-190 mV ~190mV)

- Over Charge/Discharge Current Protection

- Discharge Short-Circuit Protection

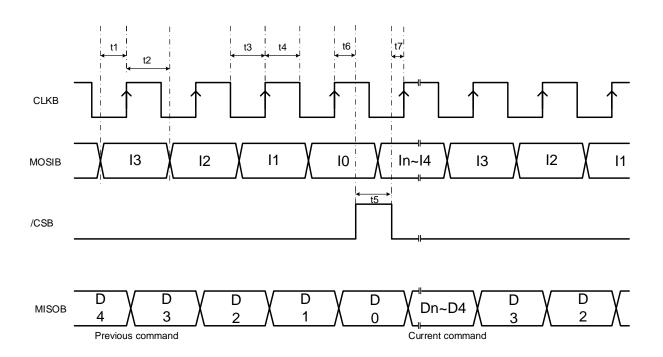

- Reliable SPI Communication (Mode3)

- 3.3V LDO Output for External Application

- External Protection N-MOSFETs

- Integrated Pre-charge/discharge Function

- Low Power Consumption

During Operation 1.5mA typ. 1.8mA Max (Power Consumption of Communication and Temperature Detection is not Included)

During Sleep 18μA typ. 20μA Max During Ship 3.2μA typ. 5μA Max

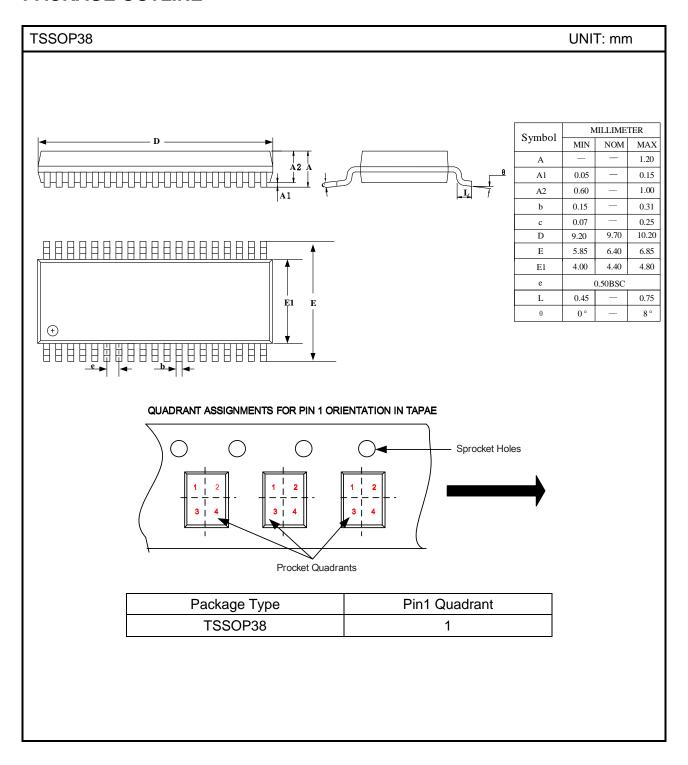

Package: TSSOP38

## **APPLICATIONS**

- Electric Bicycles, Motorcycles.

- Backup Battery Systems

- Hybrid Electric Vehicle

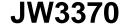

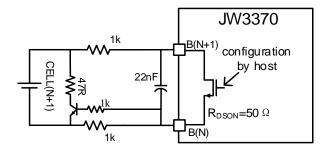

## **TYPICAL APPLICATION**

10 Cells Low Side Driver

Note: D<sub>VIN</sub> recommends using Schottky diode, witch the forward voltage (V<sub>F</sub>) is less than 0.3V.

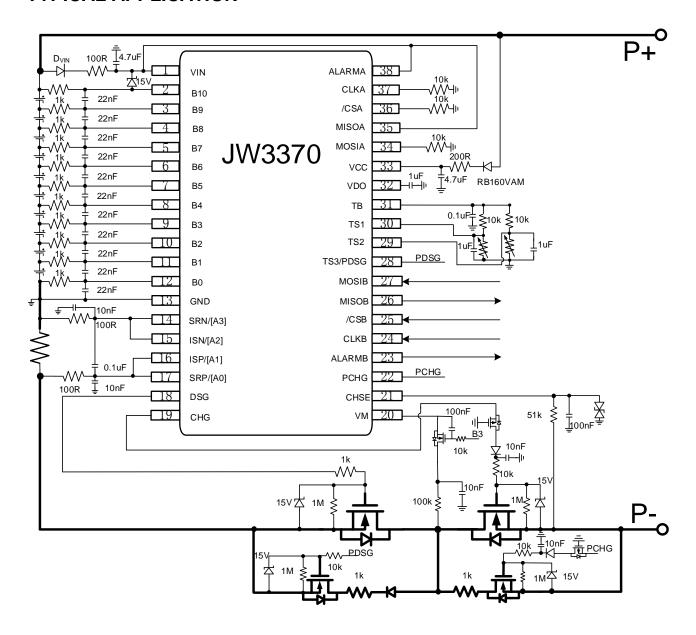

20 Cells Low Side Driver

**Note:** When the charger voltage is 30V higher than the battery voltage, there will be leakage current during charging.

$$I_{Leakage}(A) = \frac{V_{charger}(V) - V_{BAT}(V) - V_{TVS}(V)}{51k\Omega}$$

## **ORDER INFORMATION**

| DEVICE <sup>1)</sup> | PACKAGE | TOP MARKING <sup>2)</sup> |

|----------------------|---------|---------------------------|

| IVA/2270TCCODE#TDDDE | TCCOD20 | JW3370                    |

| JW3370TSSOPF#TRPBF   | TSSOP38 | YW□□□□□                   |

#### Notes:

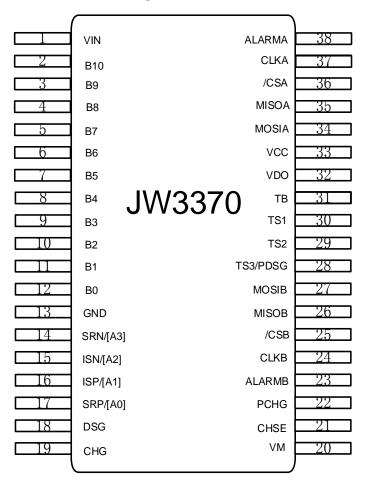

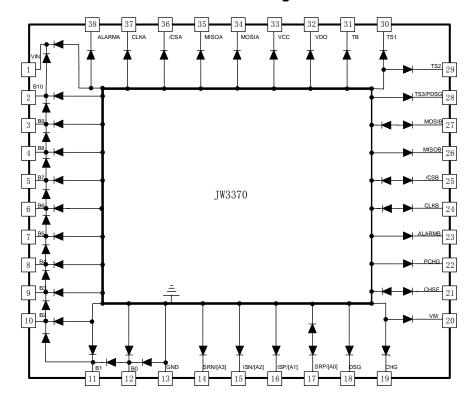

# **PIN CONFIGURATION**

## **TOP VIEW**

TSSOP38

# **ABSOLUTE MAXIMUM RATING<sup>1)</sup>**

| VIN-GND, VCC-GND                               | 0.             | 3V to 60V  |

|------------------------------------------------|----------------|------------|

| B(N)-GND N=04                                  | 0.             | 3V to 40V  |

| B(N)-GND N=510                                 | 0.             | 3V to 60V  |

| B(N)-B(N-1) N=110                              | 0.             | 3V to 20V  |

| B10-VIN                                        | 20             | V to 0.6V  |

| SRP                                            |                | 5V to 40V  |

| CHSE                                           | GND-4          | 0V to 60V  |

| VM, CHG                                        | 0.             | 3V to 60V  |

| DSG                                            |                |            |

| /CSB, CLKB, MOSIB                              | <u>[</u>       | 5V to 6.5V |

| MOSIA, /CSA, CLKA, MISOA, ALARMA               |                |            |

| All Other Pins                                 | 0.3            | 3V to 6.5V |

| Junction Temperature <sup>2)</sup>             |                | 150°C      |

| Lead Temperature                               |                | 260°C      |

| Storage Temperature                            |                |            |

| RECOMMENDED OPERATING CONDITIONS <sup>3)</sup> |                |            |

| B(N)-B(N-1) N=110                              |                | 0V to 5V   |

| VIN-GND                                        |                |            |

| Operating Junction Temperature                 | 40°C           | to +85°C   |

| THERMAL PERFORMANCE <sup>4)</sup>              | 0              | 0          |

|                                                | $	heta_{J\!A}$ |            |

| TSSOP38                                        | 86             | 19°C/W     |

## Note:

- 1) Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at any other conditions beyond those indicated under RECOMMEND OPERATION CONDITIONS.

- 2) The JW3370includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARATERISTICS**

| ITEM                                     | SYMBOL                            | CONDITION                                            | MIN. | TYP.  | MAX. | UNITS |

|------------------------------------------|-----------------------------------|------------------------------------------------------|------|-------|------|-------|

| Power Supply                             |                                   |                                                      |      |       |      |       |

| Operation voltage on VIN                 | VIN                               |                                                      | 8    |       | 50   | V     |

| Startup voltage of VIN and VCC           | V <sub>IN_START</sub>             |                                                      |      | 5.5   | 6    | V     |

| On anti-manage of MN and                 |                                   | T <sub>A</sub> =-40°C <sup>5)</sup>                  | 1.2  | 1.45  | 1.8  | mA    |

| Operation current of VIN and VCC         | I <sub>IN_O</sub>                 | T <sub>A</sub> =25℃                                  | 1.3  | 1.5   | 1.8  | mA    |

| VCC                                      |                                   | T <sub>A</sub> =85 °C <sup>5)</sup>                  | 1.4  | 1.64  | 1.9  | mA    |

|                                          |                                   | T <sub>A</sub> =-40°C <sup>5)</sup>                  | 17   | 18    | 20   | μΑ    |

| Sleep current of VIN and VCC             | I <sub>IN_L</sub>                 | T <sub>A</sub> =25°C                                 | 17   | 18    | 20   | μΑ    |

|                                          |                                   | T <sub>A</sub> =85 °C <sup>5)</sup>                  | 19   | 20    | 24   | μΑ    |

|                                          |                                   | T <sub>A</sub> =-40°C <sup>5)</sup>                  | 2.3  | 2.6   | 4    | μΑ    |

| Ship current of VIN                      | l <sub>IN_</sub> s                | T <sub>A</sub> =25℃                                  | 2.4  | 3.2   | 5    | μΑ    |

|                                          |                                   | T <sub>A</sub> =85 °C <sup>5)</sup>                  | 3.4  | 3.8   | 6    | μΑ    |

| 1.00                                     | V <sub>DO</sub>                   | No Load                                              | 3.2  | 3.3   | 3.4  | V     |

| LDO output voltage                       |                                   | I <sub>LOAD</sub> =50mA                              | 3.2  | 3.3   | 3.4  | V     |

| TI 11: 14 (0.0)()                        | .,                                | No Load                                              | 3.26 | 3.3   | 3.31 | V     |

| Thermal bias voltage (3.3V)              | V <sub>ТВ</sub>                   | I <sub>LOAD</sub> =2mA                               | 3.26 | 3.3   | 3.31 | V     |

| LDO output current limit                 | I <sub>LMT_LDO</sub>              |                                                      | 70   | 100   |      | mA    |

| LDO turn off delay time                  | tLDO_OFF <sup>5)</sup>            |                                                      |      | 1     |      | s     |

| TB output current limit                  | І <sub>LМТ_ТВ</sub>               |                                                      |      | 12    |      | mA    |

| LDO/TB over thermal warning threshold    | T <sub>LDO_WAR</sub> 5)           |                                                      | 115  | 125   | 135  | °C    |

| LDO/TB over thermal protection threshold | T <sub>LDO_PRO</sub> 5)           |                                                      | 138  | 150   | 162  | °C    |

| Thermal shutdown threshold               | T <sub>SHUTD</sub> <sup>5)</sup>  |                                                      |      | 150   |      | °C    |

| Thermal hysteresis                       | T <sub>HYS</sub> 5)               |                                                      |      | 25    |      | °C    |

| 14-BIT ADC ( for cell voltage and        | d temperature n                   | nonitor )                                            |      |       |      |       |

| Resolution of ADC                        | V <sub>VREV</sub> 5)              |                                                      |      | 0.305 |      | mV    |

| Measurement range of ADC                 | V <sub>RANGEV</sub> <sup>5)</sup> |                                                      | 0    |       | 5.0  | V     |

| Offset voltage of measurement            | Voffsetv <sup>5)</sup>            |                                                      | -0.5 | 0     | 0.5  | mV    |

| Error voltage of measurement             | V <sub>ERR</sub>                  | V <sub>CELL</sub> =2.3V~4.3V<br>T <sub>A</sub> =25°C | -7   | 5     | 7    | mV    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | _                                                                               |      |      |      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------|------|------|------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | $V_{CELL}=2.3V-4.3V$ $T_{A}=-20^{\circ}C$ $\sim 65^{\circ}C^{5)}$               | -15  |      | 15   | mV  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | V <sub>CELL</sub> =2.3V~4.3V<br>T <sub>A</sub> = - 40°C<br>~85°C <sup>5</sup> ) | -20  |      | 20   | mV  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Normal mode<br>T <sub>A</sub> =25°C                                             | 0.9  | 1    | 1.1  | MHz |

| Frequency of ADC clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | fclk                     | Normal mode<br>$T_A= -40^{\circ}C$<br>$\sim 85^{\circ}C^{5)}$                   | 0.85 |      | 1.15 | MHz |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Fast mode,                                                                      |      |      |      |     |

| Manager time of single call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ± 5)                     | Setting: Control                                                                |      | 0.04 |      |     |

| Measure time of single cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tunitv <sup>5)</sup>     | Parameter Set: bit                                                              |      | 0.64 |      | ms  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | [49:48]=0x0                                                                     |      |      |      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Fast mode,                                                                      |      |      |      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _,                       | Setting: Control                                                                |      |      |      |     |

| Measure time of 10 cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tcycle <sup>5)</sup>     | Parameter Set: bit                                                              |      | 6.4  |      | ms  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | [49:48]=0x0                                                                     |      |      |      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Fast mode,                                                                      |      |      |      |     |

| Cell balancing relaxation time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | Setting: Control                                                                |      |      |      |     |

| before cell voltage measured                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | t <sub>CB_RELAX</sub> 5) | Parameter Set: bit                                                              |      | 0.64 |      | ms  |

| , and the second |                          | [49:48]=0x0                                                                     |      |      |      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Fast mode,                                                                      |      |      |      |     |

| Temperature measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | Setting: Control                                                                |      |      |      |     |

| interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>TEMP</sub> 5)     | Parameter Set: bit                                                              |      | 64   |      | ms  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | [49:48]=0x0                                                                     |      |      |      |     |

| 16-BIT ADC ( for current monito                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r)                       |                                                                                 |      |      |      |     |

| Resolution of ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>VREC</sub> 5)     |                                                                                 |      | 6    |      | μV  |

| Measurement range of ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>RANGEC</sub> 5)   |                                                                                 | -190 |      | 190  | mV  |

| ssouroment range of ADO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VIVAIGEO                 | Vsrp-srn =                                                                      |      |      |      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | - 100mV~100mV<br>T <sub>A</sub> =25°C                                           | -150 | ±75  | 150  | μV  |

| Error voltage of measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>ERRC</sub>        | $V_{SRP-SRN} =$ - 190mV~190mV $T_{A}=25^{\circ}C$                               | -300 | ±150 | 300  | μV  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LINO                     | $V_{SRP-SRN} =$ - 100mV~100mV $T_{A}=-20~65^{\circ}C^{5}$                       | -180 |      | 180  | μV  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | $V_{SRP-SRN} =$ - 190mV~190mV $T_{A}=-20~65^{\circ}C^{5}$                       | -360 |      | 360  | μV  |

|                         |               |    |                               | $V_{SRP-SRN} =$ - 100mV~100mV $T_{A}=-40~85^{\circ}C^{5}$  | -300                          |                   | 300          | μV |

|-------------------------|---------------|----|-------------------------------|------------------------------------------------------------|-------------------------------|-------------------|--------------|----|

|                         |               |    |                               | $V_{SRP-SRN} =$ - 190mV~190mV $T_{A}=-40~85^{\circ}C^{5)}$ | -600                          |                   | 600          | μV |

| Current measure t       | ime cycle     |    | t <sub>UNITC</sub> 5)         |                                                            |                               | 132               |              | ms |

| Protection              |               |    |                               |                                                            |                               |                   |              |    |

| Over charge/            | Threshold Ran | ge | Voc/Vod                       |                                                            | 0                             |                   | 5            | V  |

| Over discharge          | Step          |    |                               |                                                            |                               | 19.53             |              | mV |

|                         | Threshold Ran | ge | toc <sup>5)</sup>             |                                                            | 0.128                         |                   | 1.92         | S  |

|                         | Step          |    |                               |                                                            |                               | 128               |              | ms |

| Over charge             | Threshold Ran | ge | toc <sup>5)</sup>             |                                                            | 0.512                         |                   | 7.68         | S  |

| delay time              | Step          |    |                               |                                                            |                               | 512               |              | ms |

|                         | Accuracy      |    |                               |                                                            | 75%*toc-<br>Step              | toc               | 125%*t       |    |

|                         | Threshold Ran | ge | t <sub>OD</sub> <sup>5)</sup> |                                                            | 0.512                         |                   | 7.68         | S  |

| Over discharge          | Step          |    |                               |                                                            |                               | 512               |              | ms |

| delay time              | Threshold Ran | ge | t <sub>OD</sub> <sup>5)</sup> |                                                            | 1                             |                   | 15.36        | S  |

| •                       | Step          |    |                               |                                                            |                               | 1024              |              | ms |

|                         | Accuracy      |    |                               |                                                            | 75%*t <sub>OD</sub> -<br>Step | top               | 125%*t       |    |

| Temperature             | Threshold Ran | ge | Vот                           |                                                            | 0                             |                   | 3.3          | V  |

| protection              | Step          |    |                               |                                                            |                               | 19.53             |              | mV |

|                         | Threshold Ran | ge | t <sub>OT</sub> <sup>5)</sup> |                                                            | 0.512                         |                   | 7.68         | S  |

| Temperature             | Step          |    |                               |                                                            |                               | 512               |              | ms |

| protection delay        |               |    |                               |                                                            | 75%*t <sub>ОТ</sub> -<br>Step | tот               | 125%*t<br>от |    |

| Disabassa               | Threshold Ran | ge | V <sub>DOI1</sub>             |                                                            | 0                             |                   | 190          | mV |